White Rabbit PTP Core (WRPC)

The White Rabbit PTP Core is an Ethernet MAC implementation capable of providing precise timing. It can be used for sending and receiving regular Ethernet frames between user-defined HDL modules and a physical medium. It also implements the White Rabbit protocol to provide sub-nanosecond time synchronization.

The White Rabbit PTP Core can operate in one of the following modes:

- GrandMaster: WR Master synchronized to an external 1-PPS and 10 MHz clock signal, propagates precise timing to other WR-compliant devices

- Master: WR Master with free-running oscillator, propagates precise timing to other WR-compliant devices

- Slave: synchronizes its internal oscillator to another WR Master device

FPGA platforms and boards supported by the White Rabbit PTP Core

| Platform | Family | Tranceiver | Reference designs | Boards |

|---|---|---|---|---|

| Xilinx | Spartan-6 | GTP-6 | spec_ref_design, svec_ref_design | SPEC, SVEC, SPEXI, .... |

| Xilinx | Virtex-6 | GTX-6 | ||

| Xilinx | Artix-7 | GTP-7 | CLBv3 | Nikhef. |

| Xilinx | Kintex-7 | GTX-7 | CLBv2, KC705 with Rabbit_FX FMC | Nikhef, Seven Solutions |

| Xilinx | Virtex-7 | GTX-7 | Nikhef, Seven Solutions | |

| Xilinx | Virtex-7 | GTH-7 | Nikhef. Not yet fully supported. Contact us (TxRx in wr-cores) |

|

| Xilinx | Kintex Ultrascale | GTH-US, GTY-US | SIS8300 | Work in progress (uses different Serdes (GTH, GTY) than Kintex, requires a new wrapper with bitslide, and making sure the Serdes is deterministic). Contact us |

| Xilinx | Zynq-7 (=Kintex-7 + ARM uP) | GTX-7 | fasec_ref_design | FASEC, Seven Solutions. |

| Altera | Arria II | GSI | ||

| Altera | Arria V | vfchd_ref_design | VFC-HD, GSI |

Fig.1: WR PTP Core external interfaces

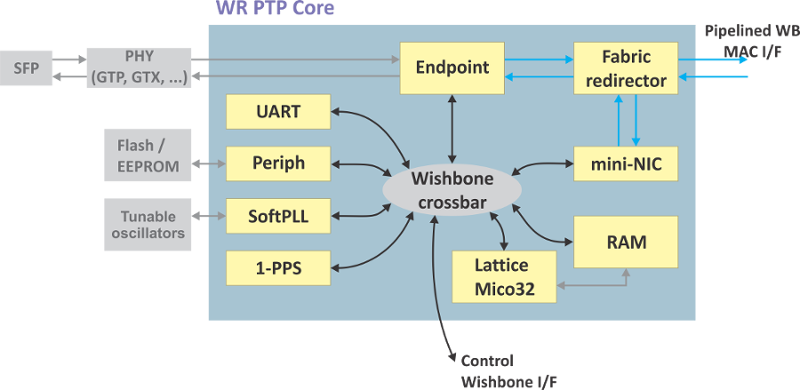

Fig.2: WR PTP Core block diagram

Releases

Documentation

- White Rabbit PTP Core User's Manual describes how to build and run the Core.

- White Rabbit PTP Core Failures and Diagnostics describes what can go wrong, how to diagnose it and how to fix it

- Default calibration values for the WR PTP Core and the WR Switch

- White Rabbit PTP Core Hands-on Training materials

Other documents

- Frequently Asked Questions about the White Rabbit PTP Core

- HDL memory map

- List of all WRPC Shell commands

- Running simple SPEC-to-SPEC White Rabbit demo

- White Rabbit Node Reference Design

- List of supported SFP transceivers

Projects that use WR PTP Core

- White Rabbit Node Core

- BTrain-over-WhiteRabbit (note extensive documentation possibly helpful for WRPC integrators)

Roadmap for WR PTP Core releases

| v4.1 | v4.2 | |

|---|---|---|

| Release date | 7/07/2017 | 19/12/2017 |

| PCIe reset bugfix for standalone operation | x | |

| Fixes and updates in HDL wrappers: | ||

| [1599], [1600], [1604] | x | |

| Fixed Rx termination scheme for Spartan6 PHY | x | |

| WRPC diagnostics over Wishbone, and host tool to read it | x | |

| Built-in default init script and VLANs support | x | |

| PPSi updated incl. fixed p2p mode | x | |

| Added mode abscal for absolute calibration | x | |

| New documentation: WRPC Failures and Diagnostics | x | |

| Vivado synthesis support | x | |

| Xilinx Zynq , Artix-7, Kintex-7 reference designs | x | |

| Fixed testbench: [1658], [1659] | x | |

| Fixed PTP calculations for links longer than 13km | x | |

| Fixed synchronization for VFC-HD board with SNMP | x | |

| New WRPC Shell command to create SDBFS image | x | |

| LLDP support | x |

Contacts

- Grzegorz Daniluk - CERN

- Tomasz Włostowski - CERN

Project Status

| Date | Event |

|---|---|

| 11-08-2012 | v2.0 Release |

| 20-12-2013 | v2.1 Release |

| 16-12-2015 | v3.0 Release |

| 15-03-2017 | v4.0 Release |

| 7-07-2017 | v4.1 Release |

| 19-12-2017 | v4.2 Release |

| 31-01-2018 | li hongming from Tsinghua University showed it is possible to use only a single external oscillator instead of two by using an internal PLL of the FPGA. Not available in a Release. |

21 September 2018