CompactRIO White Rabbit (CRIO-WR)

Project Description

CRIO-WR is a standalone White

Rabbit node

implementation on a PCB with a form factor for National Instruments

CompactRIO modules.

The board is originally derived from and keeps maximum firmware

compatibly with the established boards

SPEC and

CUTE-WR.

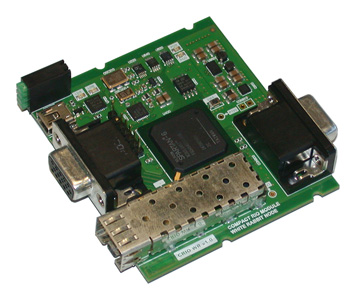

| CRIO-WR v1.0 production board | CRIO-WR module prototype |

|---|---|

|

|

Main Features

- WR node in CompactRIO format

- Complies with most CompactRIO specifications *

- Standalone WR operation (GrandMaster, Master or Slave mode)

- 10 MHz and PPS inputs (GrandMaster mode)

- 125 MHz and PPS outputs

- 6-layer PCB

- On-board power supply

- 5 V input from CompactRIO carrier

- 3.3 V and 1.2 V output

- Sleep mode

- Clocking resources

- 1x TCXO 25 MHz controlled by a DAC (used by WRPC)

- 1x VCXO 20 MHz controlled by a DAC (used by WRPC)

- 1x low-jitter frequency synthesizer/fanout with fixed configuration, Fout=125 MHz (used by WRPC)

- 1x Xilinx Spartan-6 FPGA (XC6SLX45T-3FGG484C)

- 1x SPI FLASH 32 MBit (M25P32-VMF6P)

- 1x Temperature sensor with unique ID (optionally used by WRPC)

- 1x EEPROM 64 kbit (optionally used by WRPC)

- 1x EEPROM 16 kbit (used by cRIO)

- FPGA configuration from SPI FLASH or via JTAG

- Front panel

- 1x SFP cage for fibre-optic transceiver (used by WRPC)

- 1x Connector mini USB B (USB-UART bridge, WRPC user shell)

- 1x Connector HDSUB-15 (user programmable I/O, up to 10x 3.3V / 5x LVDS)

- 4x LEDs (user programmable)

- On-board add-ons

- 1x Push button (user programmable)

- 2x LEDs (user programmable)

- 2x LEDs (power on, power good)

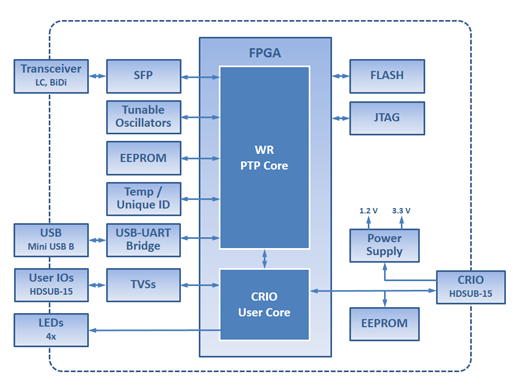

Block Diagram

CRIO-WR is based on a Spartan-6 FPGA with WR PTP Core plus the required hardware to implement a standalone WR node (see also White Rabbit Node Reference Design for more information).

The backplane connector, a dedicated power supply with sleep-mode, a

separate EEPROM for module identification parameters and an SPI plus

some glue logic in the FPGA's CRIO User Core are used for CompactRIO

functionality.

The connector at the front panel provides 10 user I/O signals, each

protected by a TVS. The I/Os are programmable depending on the

application requirements (input / output, 3.3V / LVDS, ISERDES2,

OSERDES2, IODELAY2 etc.).

The 4 LEDs at the front panel are user programmable, e.g. as status

indicators.

Product information

Downloads

- Schematic diagram

- PCB

- PCB fabrication files

- Altium project files

- Firmware - demo, FPGA Xilinx ISE v13.4 project files

- Firmware - demo, FPGA configuration files only -bitstream/PROM file

- LabVIEW - demo

- Hardware short test description

A LabVIEW driver is currently under development:

- Read / write module identification parameters

- Read status of WR-link

- Read validity of WR-timecode

- Read actual value of WR-timecode

- Read externally triggered timestamps based on WR-timecode

- Generate scheduled output pulses based on WR-timecode

*CRIO-WR complies with most CompactRIO specifications. The table below lists the known violations

| Requirement | Specification | CRIO-WR |

|---|---|---|

| Current consumption | <= 200 mA | 480 mA |

| Total inrush charge (integral of current drawn in excess of 200 mA) | <= 150uC | TBD |

| Operating power (85 ºC rated components) | <= 0.625 W | 2.4 W |

| Operating temperature range | -40 to 70 ºC | TBD |

First tests at room temperature showed no issues (CRIO-WR master with CRIO-WR slave), after 8 hours of constant operation the internal module ambient temperature is 45°C.

Releases

- Hardware: v1.0

- Firmware (demo): v0.1

- LabVIEW (demo): v0.1

Project information

- Users

- Frequently Asked Questions

- Articles

- Xilinx Xcell blog: White Rabbit module for NI’s cRIO based on Spartan-6 FPGA

Contacts

Commercial producers

- CompactRIO White Rabbit Module INCAA Computers, Netherlands.

General questions about project

- Achim Vollhardt, Physik Institut, Universitaet Zuerich, Switzerland

- David Wolf, Physik Institut, Universitaet Zuerich, Switzerland (LabVIEW)

- Daniel Florin, Physik Institut, Universitaet Zuerich, Switzerland (hardware, firmware)

- Adriaan Rijllart, CERN, Geneva, Switzerland (user)

Status

| Date | Event |

|---|---|

| 06-01-2014 | Start of project |

| 12-05-2014 | Hardware v1.0 ready for production |

| 30-06-2014 | Three v1.0 boards received from production, start testing them |

| 02-07-2014 | Some component values modified (schematic diagram / BOM v1.01) |

| 07-07-2014 | WRPC mode GrandMaster, Master and Slave functional (cRIO-WR / cRIO-WR) |

| 14-07-2014 | First tests in cRIO chassis with LabVIEW (SPI EEPROM read / write, SPI FPGA read / write) |

| 29-08-2014 | Interest from CSNS in China |

| 24-10-2014 | Tests at CERN with WR switch and cRIO-WR in slave mode reaching 8 ns jitter on time stamp |

| 07-11-2014 | One module has been sent to NI for compliance testing |

| 09-12-2014 | A first batch of 10 modules has been ordered for use at CERN |

| 15-01-2015 | EPFL Lausanne, Sergio Barreto has plans to order modules for his smart grid test bed |

| 21-04-2015 | Received the 10 modules at CERN |

| 16-06-2015 | Reaching 850 ns delay and 2 ns jitter on time stamp |

| 23-06-2015 | Meeting cRIO-White Rabbit status update and WR roadmap |

| 02-07-2015 | Shipped two modules for test at NI Hungary for ELI laser project (Extremely Light Infrastructure) |

| 07-07-2015 | An article appeared on this Xilinx forum |

| 04-02-2016 | CRIO-WR commercially available |

| 17-03-2016 | EPFL Lausanne has borrowed two modules for tests |

| 20-03-2016 | Sylvain Ravat and Antoine Kehrli of EP-DT have borrowed one module for accurate time stamping of ATLAS magnet protection events |

| 09-11-2016 | Mario Paolone of the EPFL submitted a paper to IEEE PowerTech 2017 about a cRIO-WR synchronised PMU |

| 20-04-2017 | Plans to evolve gateware to output a programmable PPS aligned square wave and update to latest White rabbit core. |

| 06-06-2017 | PPS aligned square wave output was added and update to latest White rabbit core done. |

| 08-10-2017 | At ICALEPCS 2017 the Brazilian Synchrotron Light Laboratory has shown interest to use cRIO-WR. |

| 12-03-2018 | The Brazilian Synchrotron Light Laboratory has received two cRIO-WR on loan from CERN for testing. They are placing an order to have their own. |

Adriaan Rijllart - 21 March 2018