| ... | ... | @@ -2,19 +2,18 @@ |

|

|

|

|

|

|

|

AFCK

|

|

|

|

|

|

|

|

*Please edit. The info below is from the AFC project**

|

|

|

|

|

|

|

|

The AMC FMC carrier is partially based on SPEC (supply, WR clocks)

|

|

|

|

design. It was primary designed to support quad 16 bit ADC FMC boards

|

|

|

|

for BPM back-end. Among many features, the card has very flexible clock

|

|

|

|

circuit that enables any clock source to be connected to any clock

|

|

|

|

input, including telecom clock, FMC clocks and FPGA.

|

|

|

|

design. Among many features, the card has very flexible clock circuit

|

|

|

|

that enables any clock source to be connected to any clock input,

|

|

|

|

including telecom clock, FMC clocks and FPGA.

|

|

|

|

It is very similar design to AMC FMC board, the only difference is

|

|

|

|

faster FPGA from Kintex7 family;

|

|

|

|

|

|

|

|

## Main Features

|

|

|

|

|

|

|

|

Functional specifications

|

|

|

|

|

|

|

|

- Xilinx Artix-7 200T FFG1156 FPGA

|

|

|

|

- Xilinx Kintex-7 325T FFG900 FPGA

|

|

|

|

- 2 GB DDR3 SDRAM (32-bit interface)

|

|

|

|

- 2 high pin count (HPC) slots for 2 single width mezzanines or 1

|

|

|

|

double width mezzanine

|

| ... | ... | @@ -34,9 +33,6 @@ Functional specifications |

|

|

|

- RTM connector with 8 GTP routed to it. Compatible with rtm-sfp8

|

|

|

|

module.

|

|

|

|

|

|

|

|

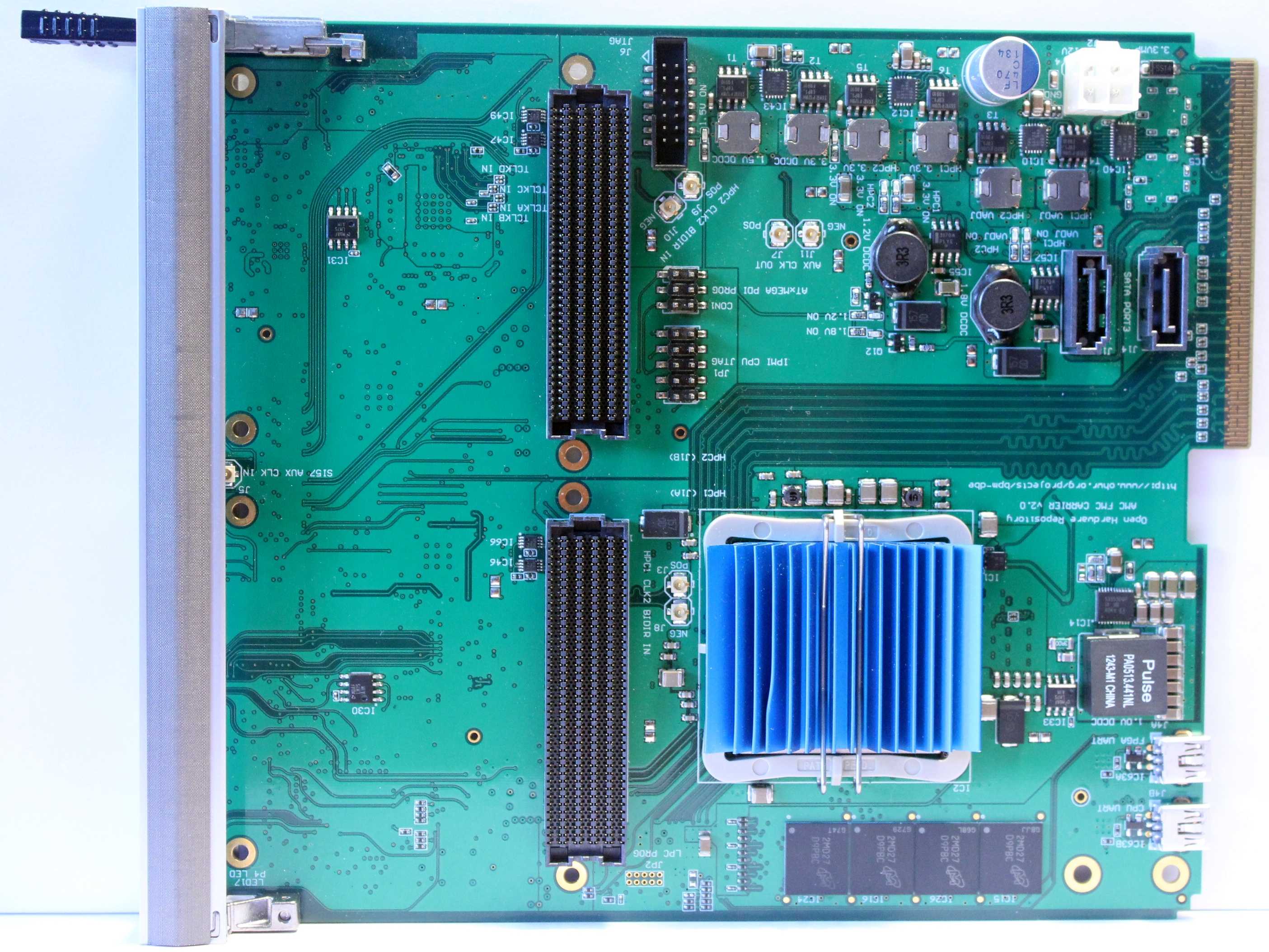

Fully assembled AFC:

|

|

|

|

|

|

|

|

|

|

|

|

# Status

|

|

|

|

|

|

|

|

<table>

|

| ... | ... | @@ -46,48 +42,8 @@ Fully assembled AFC: |

|

|

|

<td><b> Event </b></td>

|

|

|

|

</tr>

|

|

|

|

<tr class="even">

|

|

|

|

<td>23-07-2012</td>

|

|

|

|

<td>Digital back-end for Sirus BPM schematics started. Creotech is in charge of the boards design.</td>

|

|

|

|

</tr>

|

|

|

|

<tr class="odd">

|

|

|

|

<td>12-09-2012</td>

|

|

|

|

<td>First version of schematics pushed to the repository.</td>

|

|

|

|

</tr>

|

|

|

|

<tr class="even">

|

|

|

|

<td>24-09-2012</td>

|

|

|

|

<td>Proposal for cooling, carrier and backplane components placement.</td>

|

|

|

|

</tr>

|

|

|

|

<tr class="odd">

|

|

|

|

<td>09-11-2012</td>

|

|

|

|

<td>Project redefinition: backplane and enclosure will use MicroTCA.4 COTS hardware. The FPGA board should be an AMC board compliant with MTCA.4.</td>

|

|

|

|

</tr>

|

|

|

|

<tr class="even">

|

|

|

|

<td>1-04-2013</td>

|

|

|

|

<td>PCB finished.</td>

|

|

|

|

</tr>

|

|

|

|

<tr class="odd">

|

|

|

|

<td>29-04-2013</td>

|

|

|

|

<td>PCB assembled, still waiting for panels from ELMA.</td>

|

|

|

|

</tr>

|

|

|

|

<tr class="even">

|

|

|

|

<td>29-05-2013</td>

|

|

|

|

<td>PCIe works, SDRAM works, clocks work.</td>

|

|

|

|

</tr>

|

|

|

|

<tr class="odd">

|

|

|

|

<td>8-09-2013</td>

|

|

|

|

<td>Next production batch (10 pieces) of the board started. Applied several cosmetic changes but 100% backward compatibility is preserved.</td>

|

|

|

|

</tr>

|

|

|

|

<tr class="even">

|

|

|

|

<td>01-10-2013</td>

|

|

|

|

<td>Batch of 10 pcbs delivered</td>

|

|

|

|

</tr>

|

|

|

|

<tr class="odd">

|

|

|

|

<td>01-11-2013</td>

|

|

|

|

<td>All boards up and running</td>

|

|

|

|

</tr>

|

|

|

|

<tr class="even">

|

|

|

|

<td>20-03-2014</td>

|

|

|

|

<td>version 3 with RTM ready for production</td>

|

|

|

|

<td>17-03-2014</td>

|

|

|

|

<td>Schematics ready for review.</td>

|

|

|

|

</tr>

|

|

|

|

</tbody>

|

|

|

|

</table>

|

| ... | ... | |