Independent control of Si571 oscillators

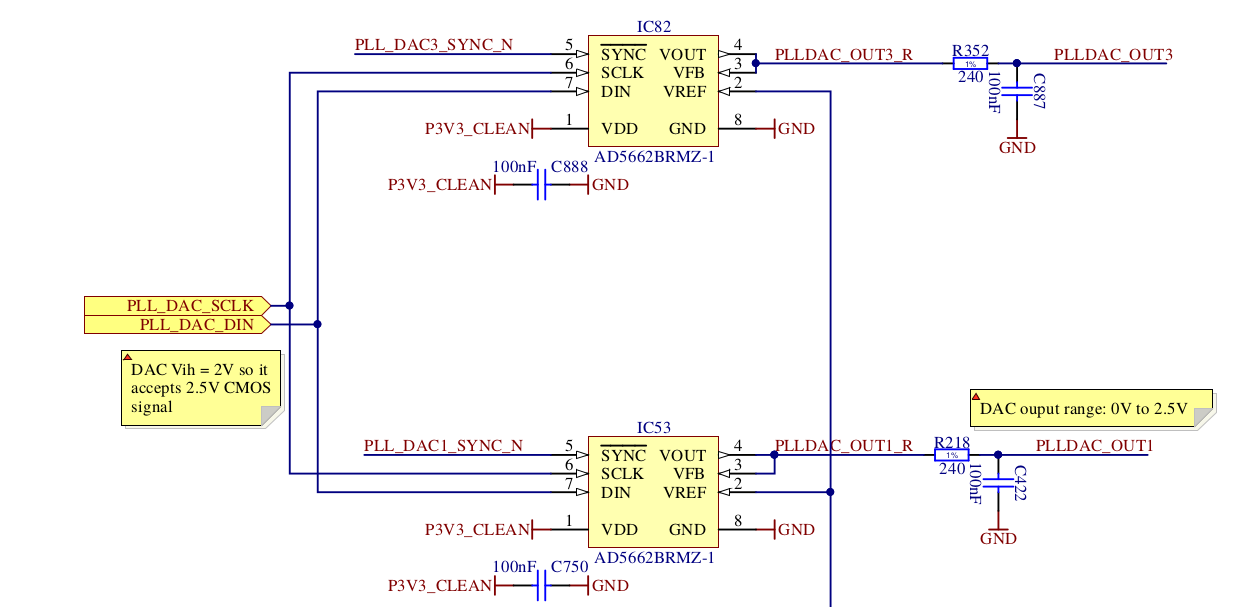

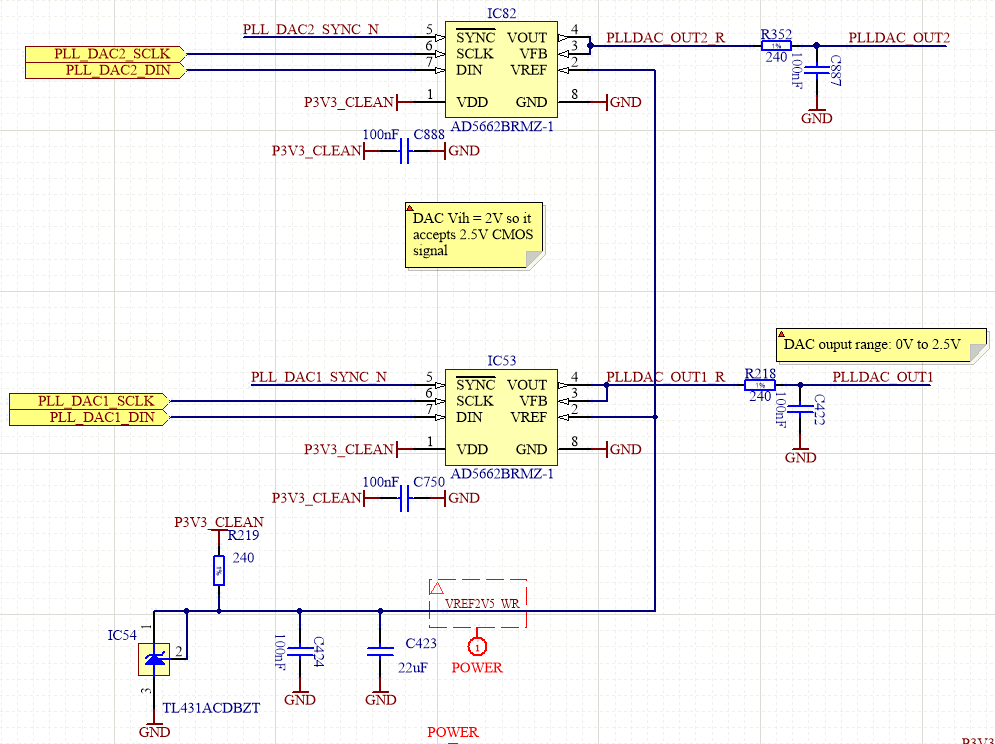

The two Si571 oscillators have shared SCK and DATA inputs, muxed via SYNC signal.

Is there a reason for that beyond saving 2 FPGA pins?

If not, and if there's no foreseen use of the free non-CC pins on banks 12 and 13, it seems worth to allow independent control of both oscillators. It makes FPGA gateware cleaner, especially for applications where these 2 clocks are not related to each other.

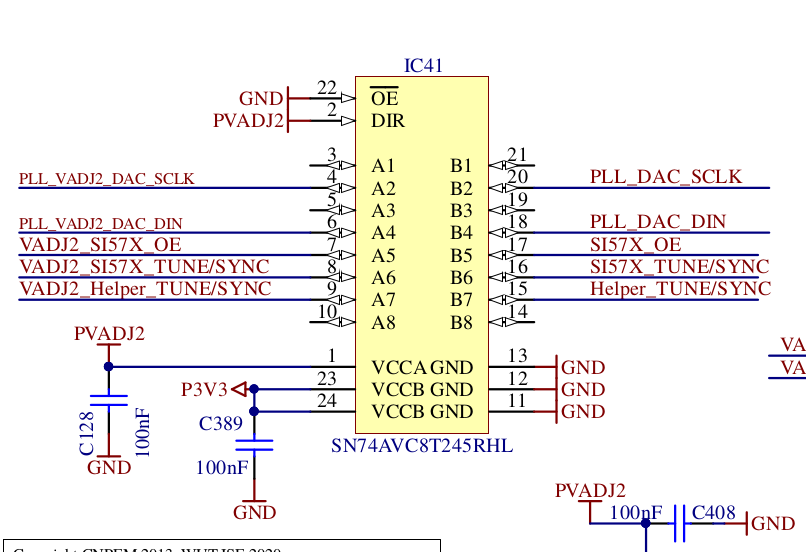

This addition seems not so inconvenient since there are free FPGA pins (IO_L6P_T0_13 and IO_25_12) and free level translator pins on IC41:

Of course, if this somehow affects WR applications there's no doubt we should ignore this suggestion.