Prototype White Rabbit tests

With support of CERN BE/CO/HT, the White Rabbit Ptp Core (WRPC) was implemented on the FASEC. Because of the use of a 7 Series SoC (the Zynq) and the use of Vivado, the existing gateware was not compatible. The Seven Solutions repository for the ZEN was forked as a starting point.

Gateware

build using wrpc-v4.2, IP + FASEC design

Ensure that

EDA-02408 is

plugged into FMC1 slot (or alternatively no cards)!

Note: merging from fix-fasecv2-viv2016.2-support to master branch will

be done once confirmed working from the WR

lab!

$ source <foo>/Xilinx/Vivado/2016.2/settings64.sh -- depends on your local installation of Vivado

$ git clone git:https://www.ohwr.org/hdl-core-lib/wr-cores.git -b fix-fasecv2-viv2016.2-support

$ cd wr-cores/

$ git submodule update --init --recursive

$ cd syn/fasec_ref_design

$ vivado -source build.tcl

wrpc IP

$ source <foo>/Xilinx/Vivado/2016.2/settings64.sh -- depends on your local installation of Vivado

$ git clone git:https://www.ohwr.org/hdl-core-lib/wr-cores.git -b fix-fasecv2-viv2016.2-support

$ cd wr-cores/

$ git submodule update --init --recursive

$ cd syn/wrc_vivado_ip

$ vivado -source build.tcl

IP gateware repo at bitbucket (wrpc-v3.0 hacked to Zynq):

https://bitbucket.org/vtpieter/wrc-1p-fasec

Note: uses public git submodules at bitbucket.org, ohwr.org and

gitlab.cern.ch; perform a git submodule update --init --recursive

first after cloning

BE/CO/HT is working on porting the wrpc-v4.0 to Zynq (Kintex FPGA),

see greg_zynq

branch

(working, one last i2c bug to fix)

FASEC project, integrating wrpc IP

Integrated at FASEC_prototype gateware: fmcs_xadc_wrpc

branch

Main modifications ref. original SevenSols:

- mainline wr-cores from wrpc added as submodule (at tag wrpc-v3.0)

- changed as much as possible gateware modules from hardcopied files in ./modules/ to the mainline ones

- LM32 software changed for same tag (ohwr wrpc-sw repo at wrpc-v3.0, make sure to update ppsi submodule)

- LM32 software header (byte-array as constant) changed for Vivado

- clock MMCME generics changed because of 25MHz VCXO clock

- top module wrc_1p_kintex7_top.vhd added, clocking based on mainline kintex7_top.vhd

- WishBone to AXI4-Lite bridge added to access all wrpc internal registers (from submodule https://gitlab.cern.ch/te-abt-ec/hdl_lib)

For loading new gateware, please do the following:

# modprobe -r fasec_hwtest.ko

# cat foo.bit > /dev/xdevcfgGateware resource utilisation of the wrpc IP alone

Device: 7z030ffg676-2

Commit: 985632bba306fab041b4ad073b35fe424ec655b3

+----------------------------+------+-------+-----------+-------+

| Site Type | Used | Fixed | Available | Util% |

+----------------------------+------+-------+-----------+-------+

| Slice LUTs* | 5553 | 0 | 78600 | 7.06 |

| LUT as Logic | 5531 | 0 | 78600 | 7.04 |

| LUT as Memory | 22 | 0 | 26600 | 0.08 |

| LUT as Distributed RAM | 8 | 0 | | |

| LUT as Shift Register | 14 | 0 | | |

| Slice Registers | 5671 | 0 | 157200 | 3.61 |

| Register as Flip Flop | 5671 | 0 | 157200 | 3.61 |

| Register as Latch | 0 | 0 | 157200 | 0.00 |

| F7 Muxes | 28 | 0 | 39300 | 0.07 |

| F8 Muxes | 1 | 0 | 19650 | <0.01 |

+----------------------------+------+-------+-----------+-------+Software

All is available in the following repository (https://gitlab.cern.ch/te-abt-ec/FASEC_petalinux), branch fasec_hwtest (confirmed?). Repo is not very clean, will be done once the swap to BuildRoot or Yocto is made.

- lm32 software loader (based on spec-sw loader):

# wrpc_swload foo - picocom for the wr-shell:

# picocom /dev/ttyUL1 - check gateware bitstream commit id (see

https://gitlab.cern.ch/te-abt-ec/FASEC_prototype/commits/fmcs_xadc_wrc):

# peek 0x43c3001c

wrpc-sw

See https://www.ohwr.org/project/wr-cores/wikis/current-release

Ensure the installation of readline-devel package (yum, zypper,

etc.)

$ git clone git:https://www.ohwr.org/hdl-core-lib/wr-cores/wrpc-sw.git ; cd wrpc-sw/

$ git submodule update --init

$ export CROSS_COMPILE="<foo>/lm32_toolchain/lm32/bin/lm32-elf-"

$ make menuconfig && make

$ scp wrc.bin root@cfe-865-fids2:Ptp tests

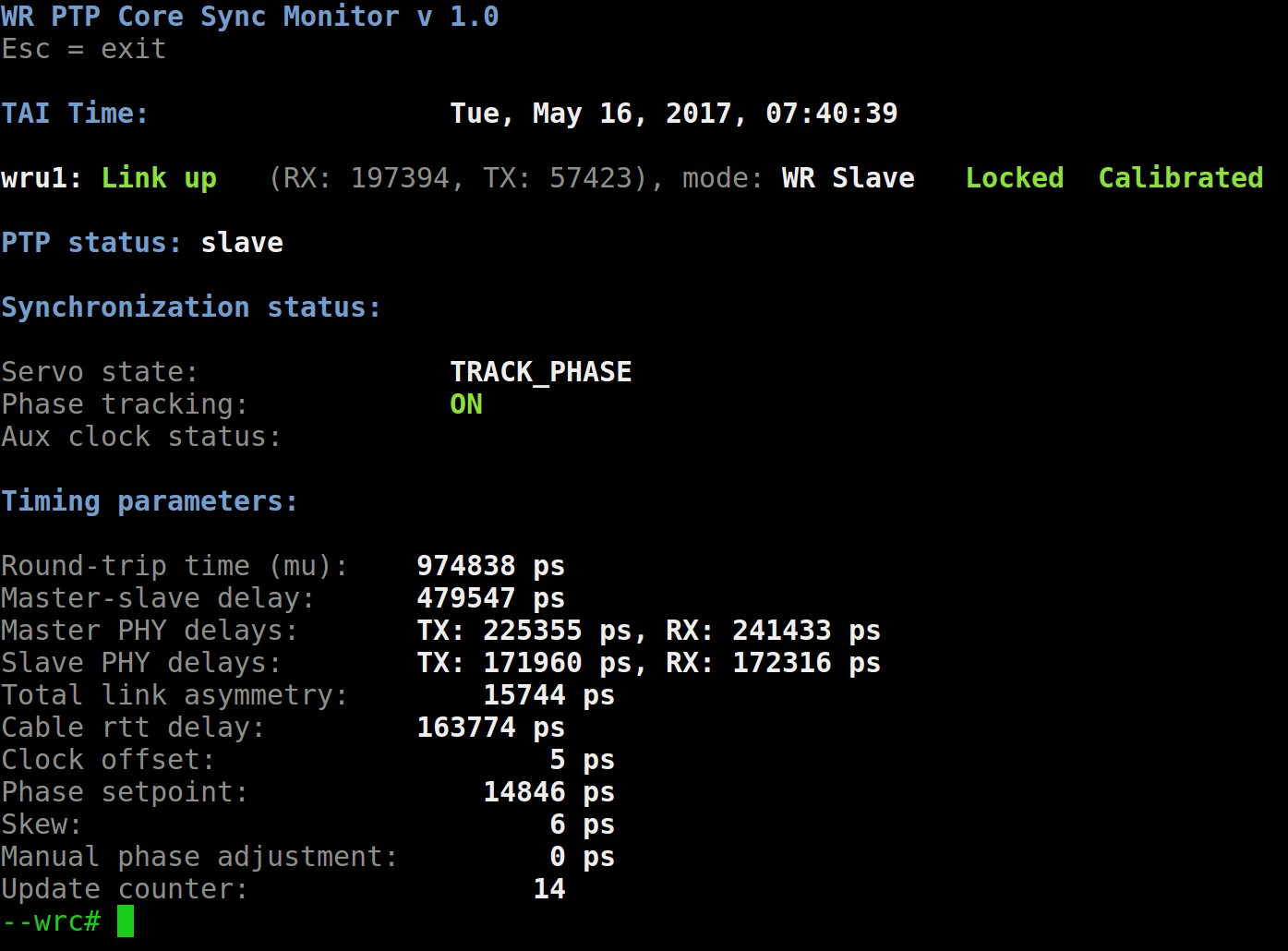

Screenshots after ~24h running.